| ← DO-254 Coverage by Linty Rules | Home | Linty HDL Designer for VS Code → |

Release Notes

Table of Contents:3.1.0

Released on May 18th, 2024.

Release Notes

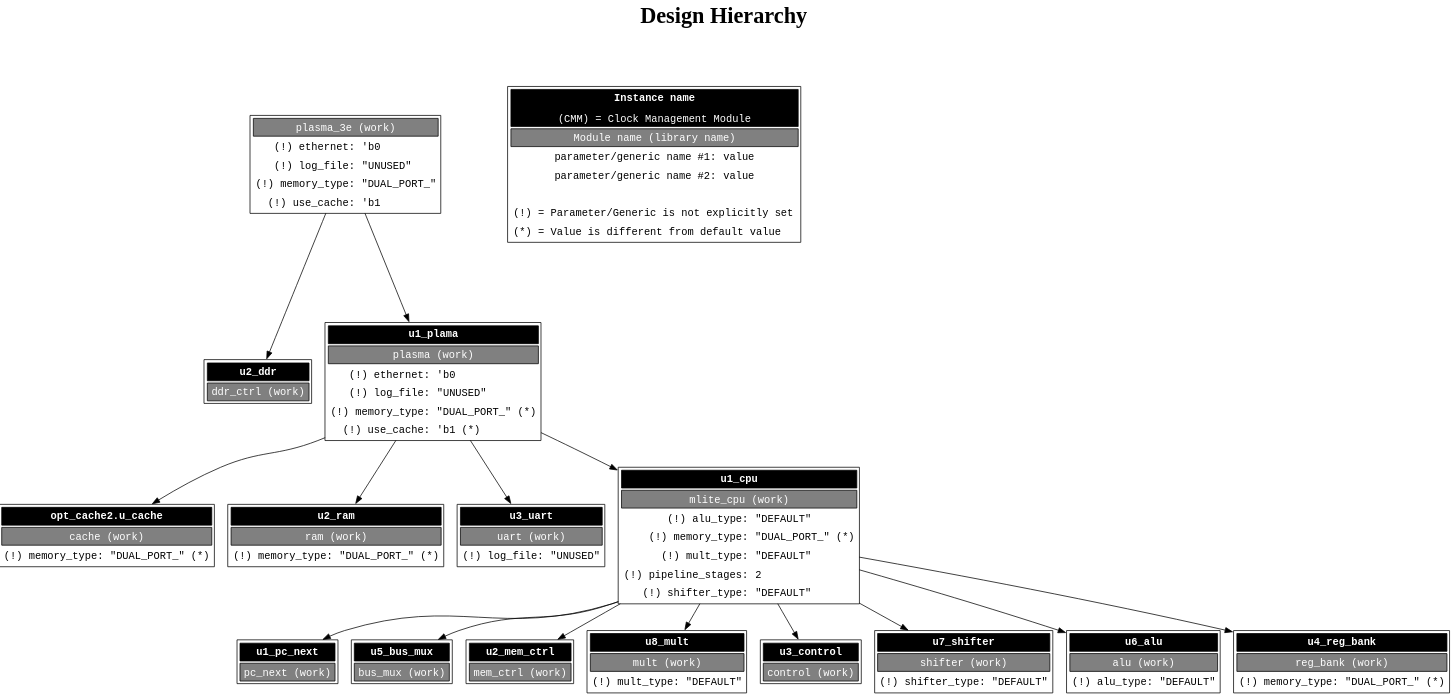

This release focuses on architecture with new rules and design hierarchy graph in Linty HDL Designer. It also provides the ability to generate documentation as HTML.

Built on SonarQube 10.5.1.

New rules

- VHDL316 - An entity should not have too many ports

- VHDL317 - A function or procedure should not have too many parameters

- VHDL318 - Generics should not define default values

- VHDL1073 - All assertions failing as note should be reviewed

- VHDL1074 - All assertions failing as warning should be reviewed

- VHDL1075 - All assertions failing as error should be reviewed

- HDL1012 - A module should not depend on too many other modules

- HDL1015 - Clock management module should be instantiated in top module

Rules that now apply to VHDL, Verilog/SystemVerilog and mixed-language designs

- VHDL1055 => HDL1013 - All clocks should be generated within a unique clock management module

- VHDL1056 => HDL1014 - Clock management module should comply with a naming convention

Upgrade Notes

Activate HDL1013 and HDL1014 to replace removed VHDL1055 and VHDL1056 rules.

3.0.0

Released on February 8th, 2024.

Release Notes

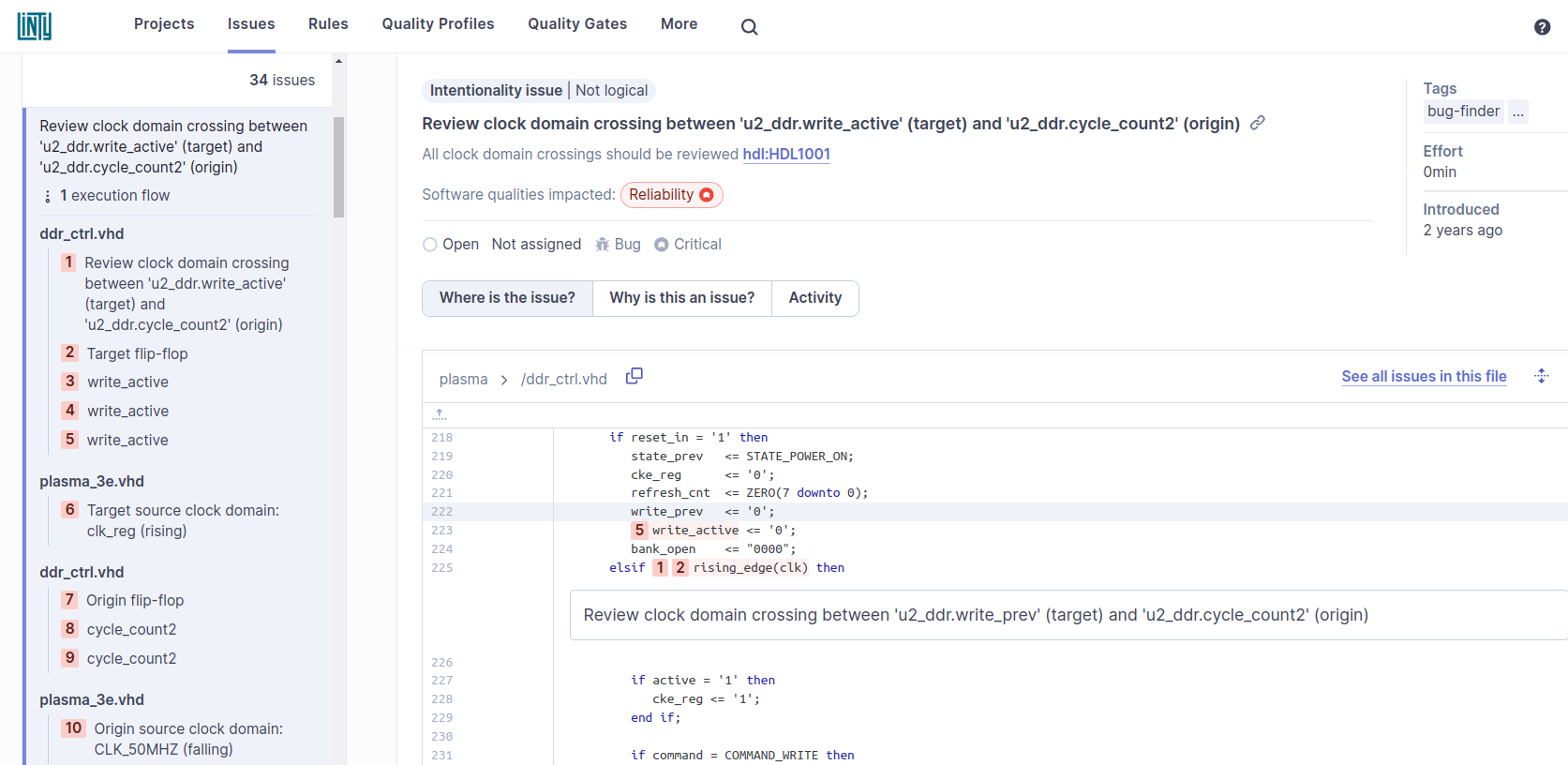

Linty detects all clock domain crossings (CDC). You can now easily browse, investigate, accept or fix any clock domain crossing.

Built on SonarQube 10.3.0.

New rules

- HDL1000 - All clock domains should be reviewed

- HDL1001 - All clock domain crossings should be reviewed

- HDL1004 - Top-level input ports should not be used within multiple clock domains

Rules that now apply to VHDL, Verilog/SystemVerilog and mixed-language designs

A new language has been created: HDL. HDL rules apply to VHDL, Verilog/SystemVerilog and mixed-language designs.

The following rules have been extended to apply to VHDL and Verilog/SystemVerilog and mixed-language designs. You should activate those rules in replacement of the related (and removed) VHDL/Verilog rules:

- VHDL1054 => HDL1002 - The number of clock domains per design should be as low as possible

- VHDL1048 => HDL1003 - Combinatorial loops should be removed

- VHDL1000 => HDL1005 - All input ports should be connected

- VHDL1001 => HDL1006 - All output ports should be connected

- VHDL1002 => HDL1007 - All inout ports should be connected

- VHDL1004 => HDL1008 - All output signals of top-level module should be registered

- VHDL1016 => HDL1009 - All output signals of low-level modules should be registered

- VHDL1017 => HDL1010 - Output signals should not be constant

- VHDL1018 => HDL1011 -Ports should not be directly connected

- VHDL177 and VERILOG007 => HDL001 - Files should contain an empty new line at the end

- VHDL179 and VERILOG006 => HDL002 - End-line characters should be consistent

- VHDL178 and VERILOG010 => HDL003 - Lines should not end with trailing whitespaces

- VHDL034 and VERILOG011 => HDL004 - Tabulation characters should not be used

- VHDL017 and VERILOG009 => HDL005 - Lines should not be too long

Linty Scanner adds compatibility to Windows and Mac

Linty analyses can now be run from Linux, Windows and Mac machines built on AMD, Intel or ARM processors.

Upgrade Notes

Please, ask for a new license key before upgrading to this latest version.

2.1.0

Released on November 25th, 2023.

Release Notes

You can now check more than 200 rules on your VHDL code.

Built on the latest SonarQube 10.3.0.

VHDL

12 new rules have been added:

- VHDL1063 - Latches should be removed

- VHDL1064 - Choices outside of range should be removed

- VHDL1065 - Choices should not overlap

- VHDL1066 - Objects of different lengths should not be compared

- VHDL1067 - Range should not be empty

- VHDL1068 - Functions should always return a value

- VHDL1069 - Signals and variables should be assigned a value before being used

- VHDL1070 - Clock names should not contain frequency information

- VHDL305 - “while” loops should not be used for synthesis

- VHDL306 - Only one single architecture per entity should be defined

- VHDL307 - Code should be properly commented

- VHDL308 - Variables should not be used

VHDL187 has been split into three rules to allow different naming conventions for for, if and case generate

statements:

- VHDL187 - “for” generate statement labels should comply with a naming convention

- VHDL309 - “if” generate statement labels should comply with a naming convention

- VHDL310 - “case” generate statement labels should comply with a naming convention

Browse all new rules.

Upgrade Notes

- VHDL168 rule has been removed. Activate its replacement that is able to deal with ranges: VHDL1065 - Choices should not overlap

2.0.0

Released on September 19th, 2023.

Release Notes

Linty now fully supports multi-language (VHDL and Verilog/SystemVerilog) projects.

Built on the latest SonarQube 10.2.0 version with support of Clean Code attributes.

VHDL

10 new rules have been added, most of them around clock and reset domains:

- VHDL1054 - The number of clock domains per design should be as low as possible

- VHDL1055 - All clocks should be generated within a unique clock management module

- VHDL1061 - Clock names should be preserved across the design

Browse all new rules.

Upgrade Notes

- Request a new licence key before upgrading

- Update the following property keys if you set them for some of your projects:

sonar.vhdl.topLevelEntity=>sonar.hdl.topModulesonar.vhdl.file.simulationPaths=>sonar.hdl.file.simulationPathssonar.vhdl.yosys.hierarchyScriptPath=>sonar.bugfinder.hierarchyScriptPathsonar.vhdl.yosys.readScriptPath=>sonar.bugfinder.readScriptPathsonar.vhdl.yosys.workdir=>sonar.bugfinder.workdir

1.2.0

Released on July 4th, 2023.

Release Notes

Built on the latest SonarQube 10.1.0 version.

It is now possible to add custom plugins to the Linty platform.

VHDL

Linty VHDL now highlights, in gray, pieces of code that are not synthesized, adds four new rules:

- VHDL1050 - Unused entities should be removed

- VHDL1051 - Unused architectures should be removed

- VHDL1052 - Unused generate blocks should be removed

- VHDL1053 - A signal should not be used as both a reset and an enable

and improves existing rules with knowledge of unused code.

Verilog

This version integrates BugFinder for Verilog with its first rule: VERILOG1000 - Unused modules should be removed and adds design graph of each module.

Upgrade Notes

Split your build.ys file into read.ys and hierarchy.ys. Replace read -vhdl <my_file>

with verific -vhdl <my_file>. See Scan Your Code for further details.

Two distributions of the linty-server Docker image are now available:

- Based on SonarQube Community Edition without branch and pull request support

- Based on SonarQube Developer Edition with branch and pull request support

1.1.0

Released on April 26th, 2023.

Release Notes

Built on the latest SonarQube 10.0.0 version.

VHDL

This version adds two new rules:

- VHDL1048 - Combinatorial loops should be removed

- VHDL1049 - An entity should not use multiple clocks

And generates graphical representations of the design. It is nice, for instance, to easily spot combinatorial loops.

Upgrade Notes

Follow uprade guide.

1.0.0

Released on March 9th, 2023.

Release Notes

First official release of the Linty Server as Docker image.

VHDL

This version includes BugFinder, a new powerful engine to detect bugs based on synthesized code

analysis. BugFinder rules are tagged as bug-finder).

There are 47 of them in this first version. Here are some of them:

- VHDL1001 - All output port of an entity should be connected

- VHDL1004 - All output signals of top-level entity should be registered

- VHDL1017 - Output signals should not be constant

Browse all of them on our demo instance.

Lots of rules have been added or improved. Some rules also changed ID because they were re-implemented with BugFinder. Thus, we highly recommend you to review your quality profile(s) to (re)activate and configure new rules.

| ← DO-254 Coverage by Linty Rules | Home | Linty HDL Designer for VS Code → |